Addressing Modes

Welsh Centre for Printing and Coatings

Tuesday November 26, 2024

Introduction

In this week’s lecture, you will learn more about assembly language and the diverse ways to access data dependent on what it is and where it is stored.

This is based around a concept known as addressing modes.

Topics discussed

In this section we will review a number of different addressing modes relevant to the Atmel ATMega328 Microcontroller including, inherent, immediate, direct, indirect and relative.

Contents

What is an addressing mode?

- An addressing mode is a way in which an operand is specified in an instruction and defines how the CPU finds it.

- There are different ways in which an operand may be specified in an instruction depending on what it is and where it is located.

- Some operations require no operands and the data to be operated on is implied, in other cases operands can be constants, variables, arrays and memory locations – this is where addressing modes are used.

Figure 1: The six addressing modes of an AVR processor.

- The memory address where data is stored is called the effective address of the operand and the addressing mode refers to the way in which the operand is specified and how the CPU accesses it.

Addressing modes on the Atmel ATmega328

The AVR® Enhanced RISC microcontroller supports powerful and efficient addressing modes for access to the program memory (Flash) and Data memory (SRAM, Register file, I/O Memory, and Extended I/O Memory).

The Atmel ATmega328 microcontroller makes use of the following addressing modes:

- Section 2.1: Inherent/Implied Addressing

- Section 2.2: Register Direct (single and two-register) Addressing

- Section 2.3: I/O Direct Addressing

- Section 2.4: Data Direct Addressing

- Section 2.5: Immediate Addressing

- Section 2.6: Data Indirect Addressing

- Section 2.7: Relative Addressing

- Program Addressing (Not covered)

Inherent Addressing Mode

For instructions that use inherent addressing, sometimes called implicit or implied addressing, the operands are not explicitly specified but are implied by the instruction1.

Examples of inherent addressing

| Mnemonic | Operands | Decription |

|---|---|---|

CLZ |

- | Clear Zero Flag in SREG |

SEI |

- | Global Interrupt Enable |

CLI |

- | Global Interrupt Disable |

SES |

- | Set Sign Bit in SREG |

CLS |

- | Clear Sign Bit in SREG |

SEV |

- | Set Two’s Complement Overflow bit in SREG |

CLV |

- | Clear Two’s Complement Overflow bit in SREG |

SET |

- | Set T bit in SREG |

CLT |

- | Clear T bit in SREG |

SEH |

- | Set Half Carry Flag in SREG |

CLH |

- | Clear Half Carry Flag in SREG |

Register Direct Addressing

For these operators, the operands are contained in registers in the register file. There are single register operators which operates on and returns the result to the destination register, known as Rd2.

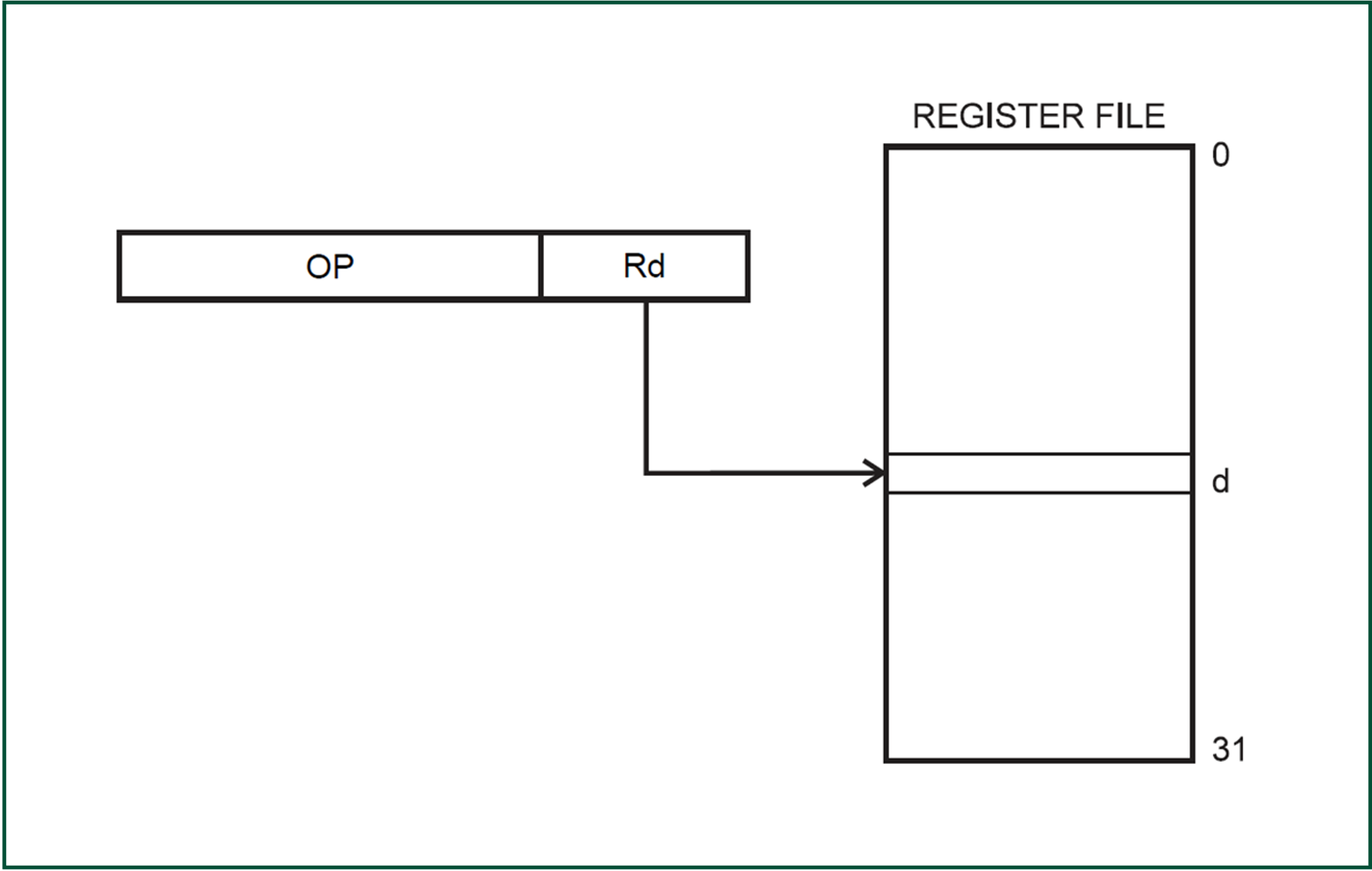

Single Register Addressing (Rd)

For instructions that use single direct register addressing, the operand is contained in the destination register Rd as illustrated in Figure 2.

Figure 2: Illustrating single register direct addressing: d is the register number and Rd is source of the operand and the destination of the result.

Examples

Two Register Addressing (Rd, Rr)

Figure 3: Illustrating register direct addressing with two registers: d is the source of the first operand, r is the source of the second operand. The result overwrites the data in register d.

Examples

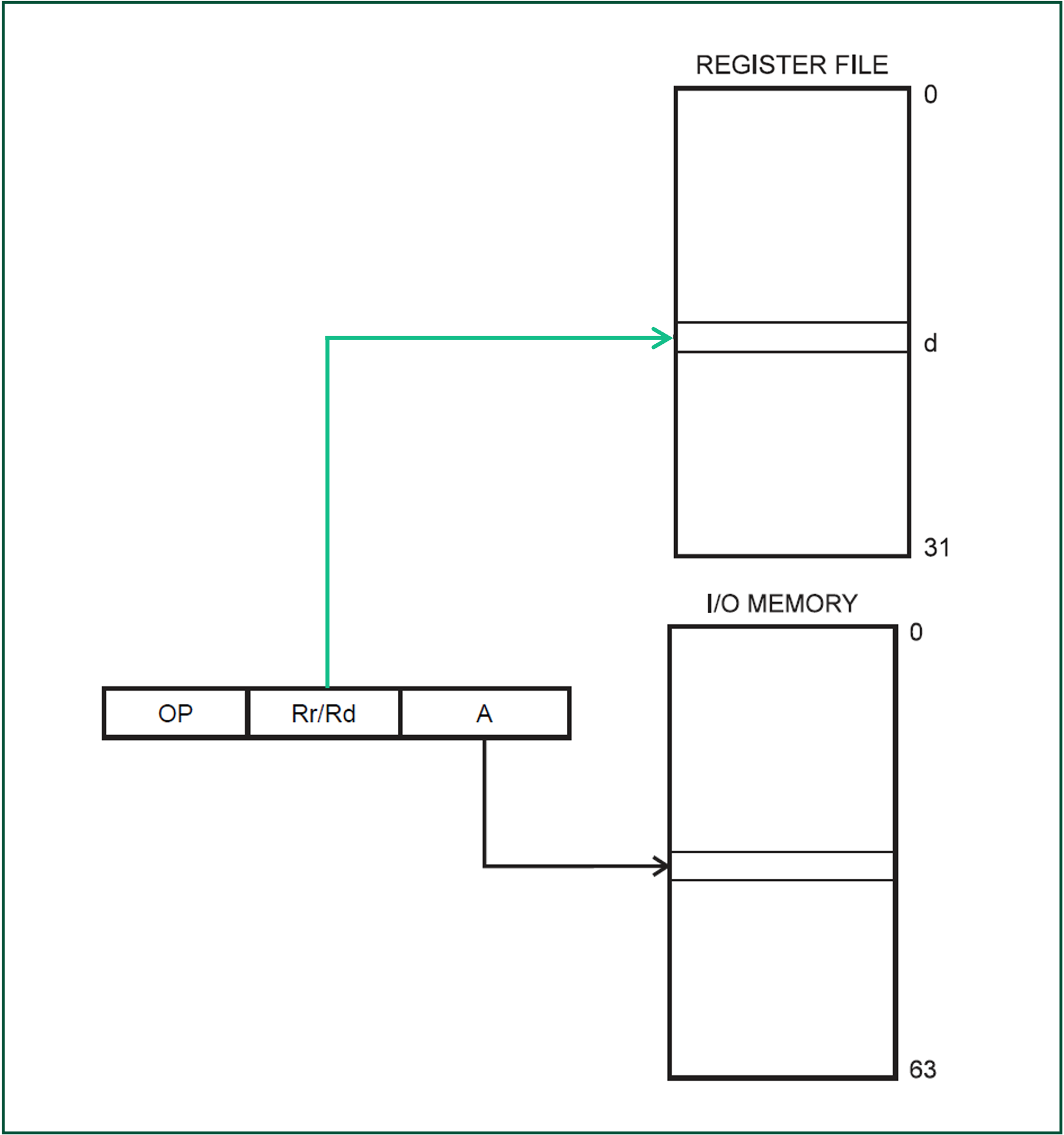

I/O Direct Addressing

Within the user data space there are 64 I/O registers as well as 160 Extended I/O registers. The first 64 of these can be accessed using instructions such as IN and OUT using I/O direct addressing mode. In I/O direct addressing mode the operands contain the address A of one of the lower 64 I/O locations and a source (Rr) or destination register (Rd). This is illustrated in Figure 4.

Figure 4: Illustrating I/O direct addressing: the source (or destination) will be from an I/O register. The destination (or source) will be one of the general purpose registers.

Examples4

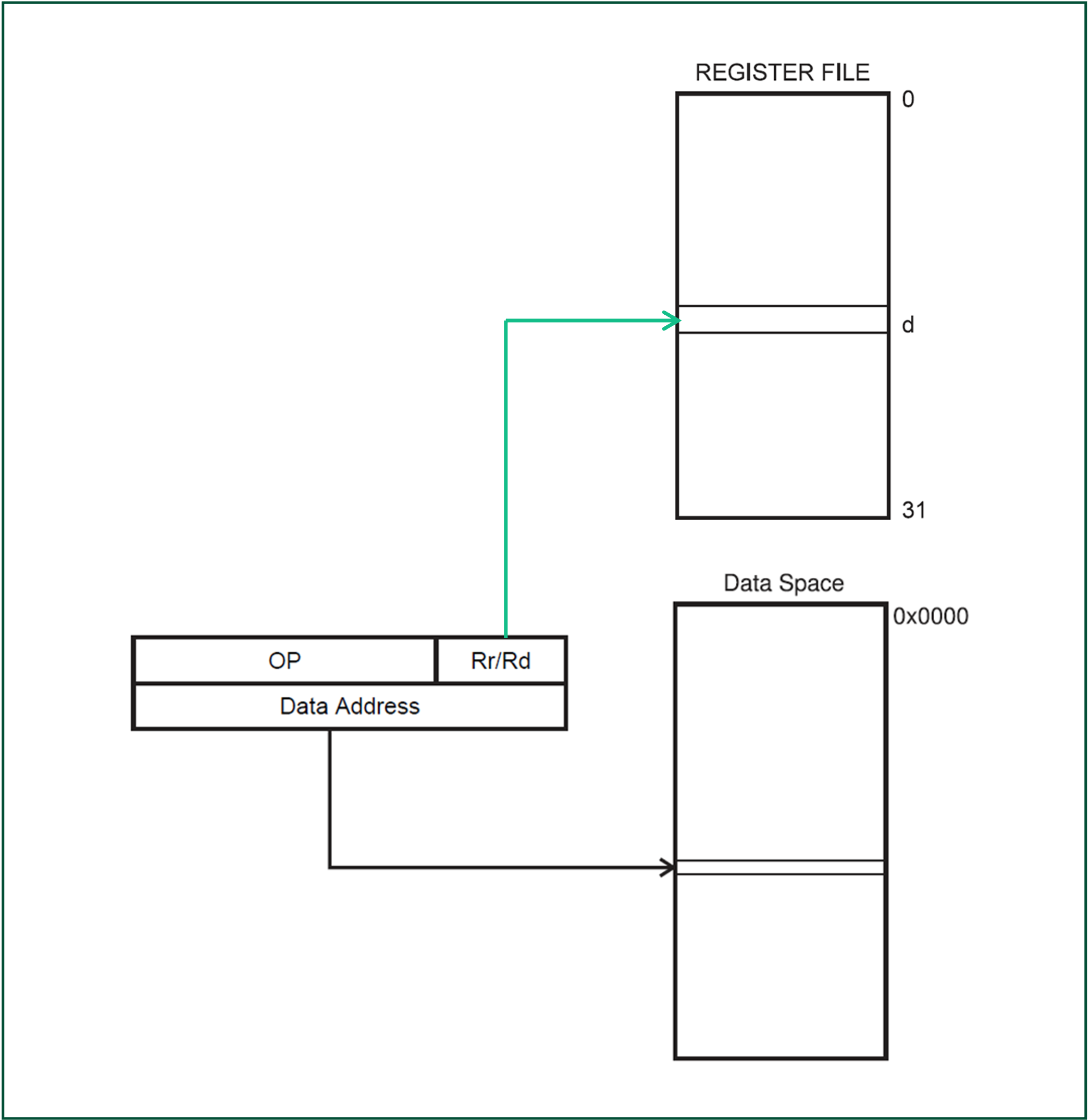

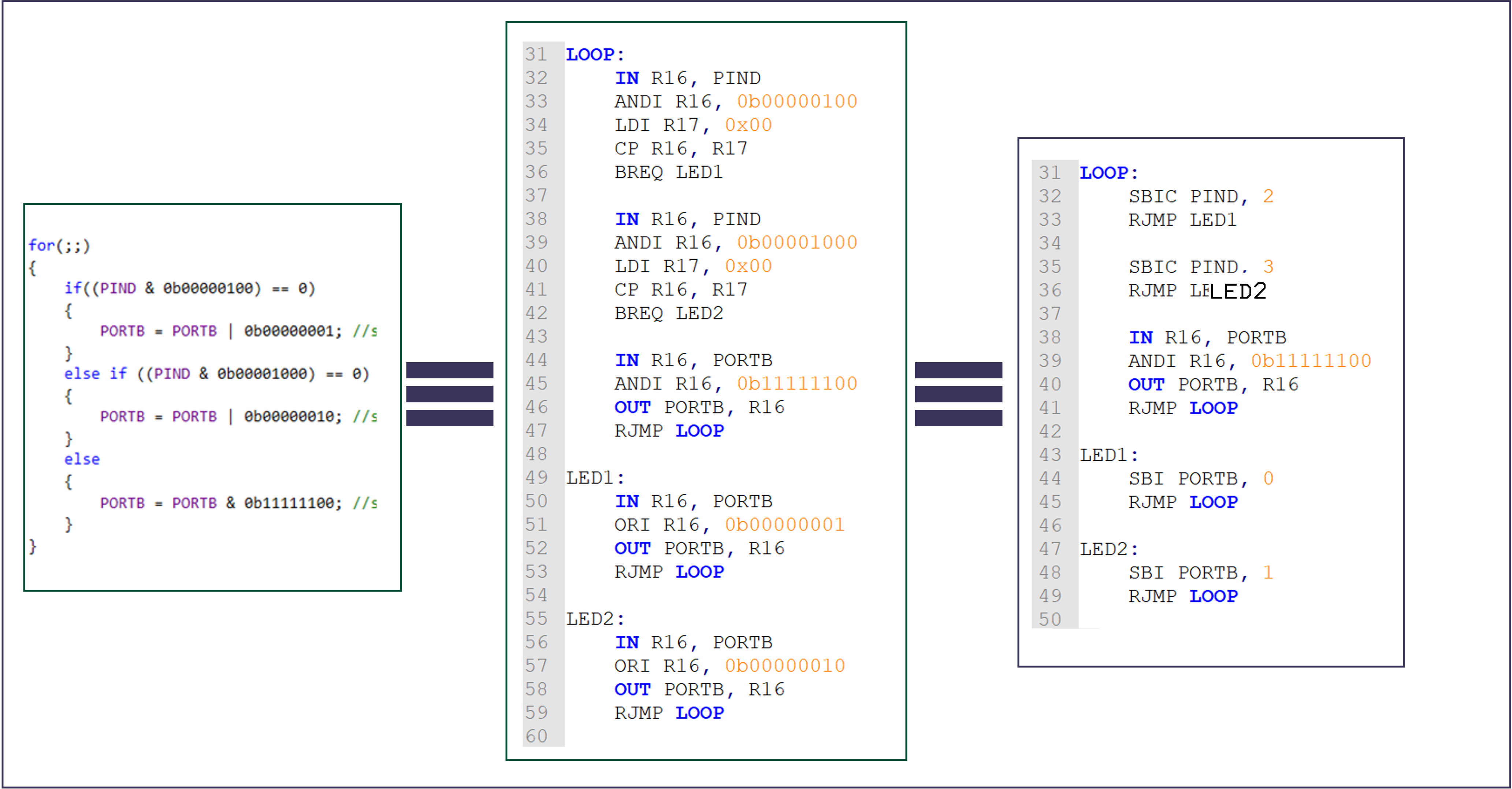

Data Direct Addressing

Instructions that use direct data addressing are two words (32-bits) in length, the first operand, Rr/Rd is one of the general-purpose registers and the second is 16-bit Data Address contained in the 16 LSBs of the two-word instruction. This is illustrated in Figure 5.

Figure 5: Illustrating data direct addressing: the source (or destination) will be in memory. The destination (or source) will be one of the general purpose registers.

Examples

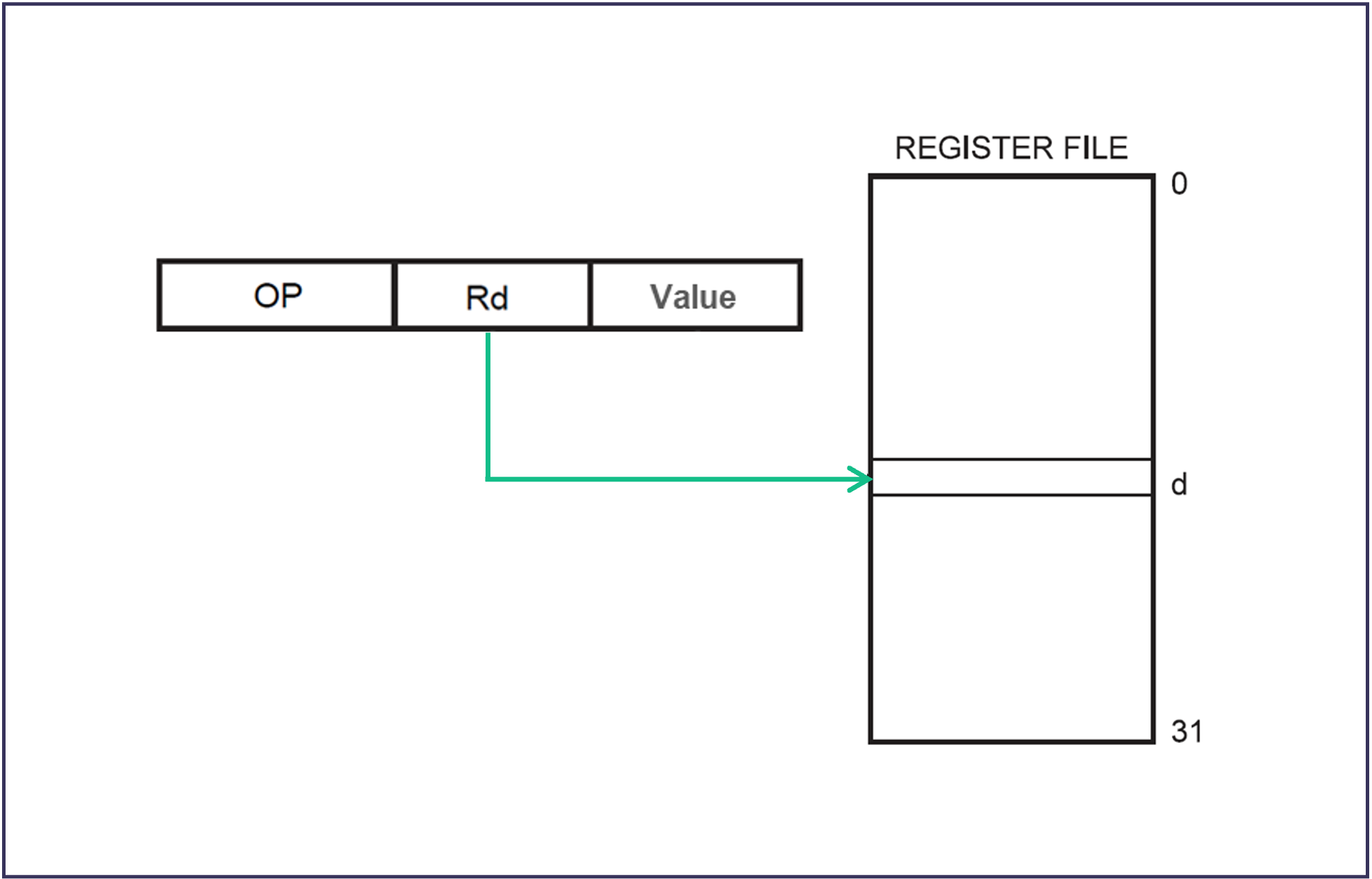

Immediate Addressing

Figure 6: Illustrating immediate addressing: the destination will be an one of the general purpose registers. The source will be a data value given in the instruction.

Examples

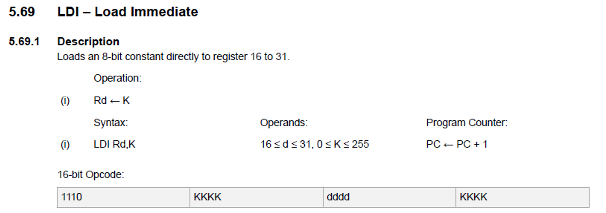

Immediate vs Data Direct Addressing

Instructions that use immediate addressing, take one clock-cycle to complete.

For example LDI - load immediate:

Instructions that use register or data direct addressing, take two clock-cycles to complete.

For example LDS - load from store needs to load the operator and decode the register address, then load data from the data space into the register.

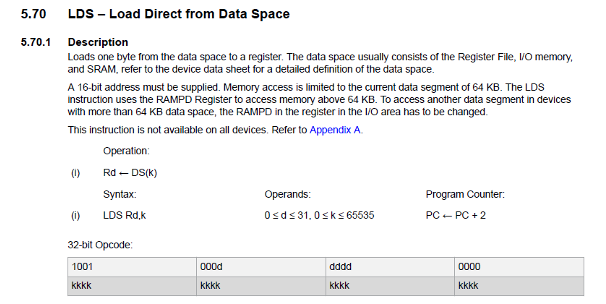

Data Indirect Addressing

With instructions that use indirect data addressing the operand address is the contents of one of the X- Y- Z-pointer registers. This is illustrated in Figure 7.

Figure 7: Illustrating indirect data addressing in which two registers provide the address in memory of the operand.

Examples

Indirect Data Addressing with Displacement

As with indirect data addressing, the microcontroller makes use of the Y and/or Z pointers with an additional displacement to access data stored in the data space.

This is the best way to access an array of data and is illustrated in Figure 8.

Figure 8: Illustrating indirect direct addressing with displacement.

Examples

Indirect Data Addressing with Increment/Decrement

Indirect Data Addressing mode also supports Post-increment and Pre-decrement addressing.

- With Data Indirect Addressing with Post-increment, the X-, Y-, or the Z-pointer is incremented after the operation.

- The operand address is the content of the X-, Y-, or the Z-pointer before incrementing.

- With Data Indirect Addressing with Pre-decrement, the X,- Y-, or the Z-pointer is decremented before the operation.

- The operand address is the decremented contents of the X-, Y-, or the Z-pointer.

Examples

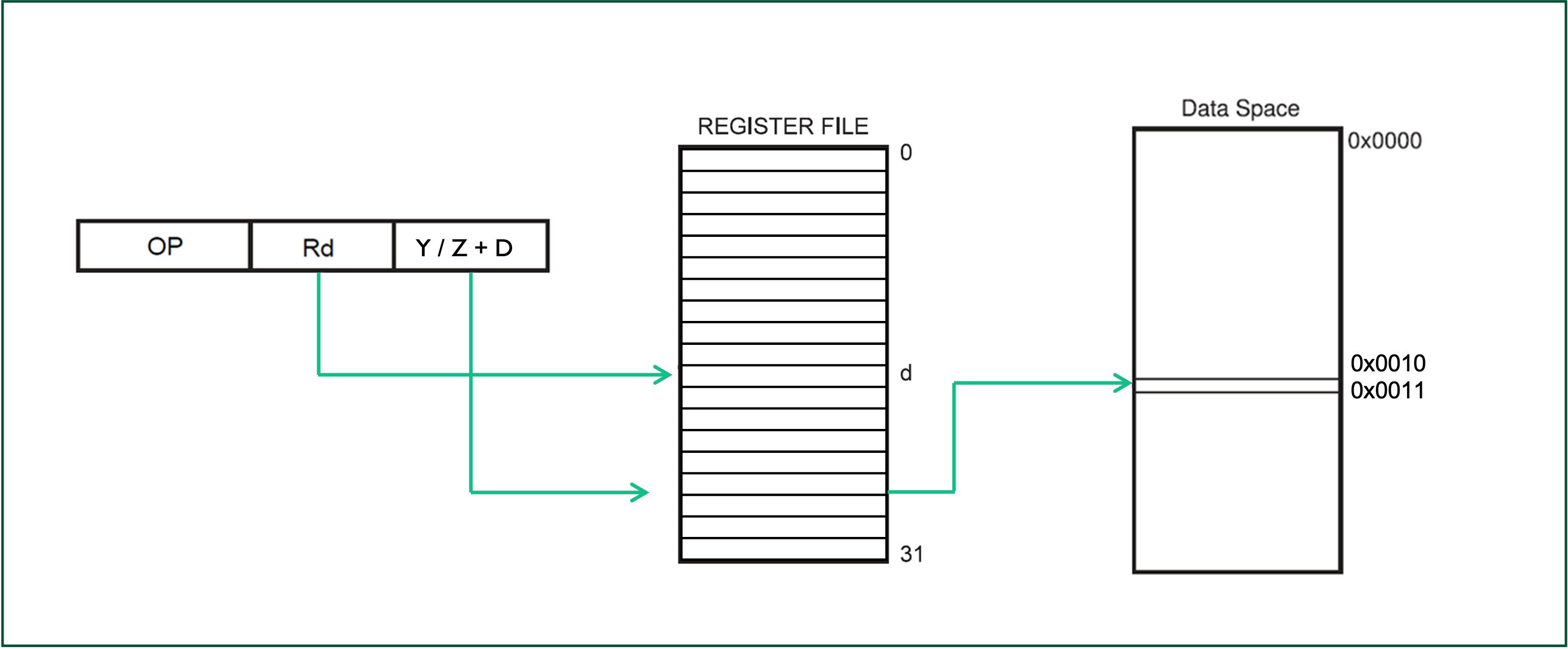

Relative Addressing

With relative program memory addressing the operand contains a signed 12-bit offset value which during execution is added to the program counter to change the flow of the program.

The destination of the branch (effective address) instruction is calculated by adding the signed byte following the opcode (-2048 to +2047) to the PC content. This is illustrated in Figure 9.

Figure 9: Illustrating relative addressing which adjusts the program counter and is typically used for branching.

Examples

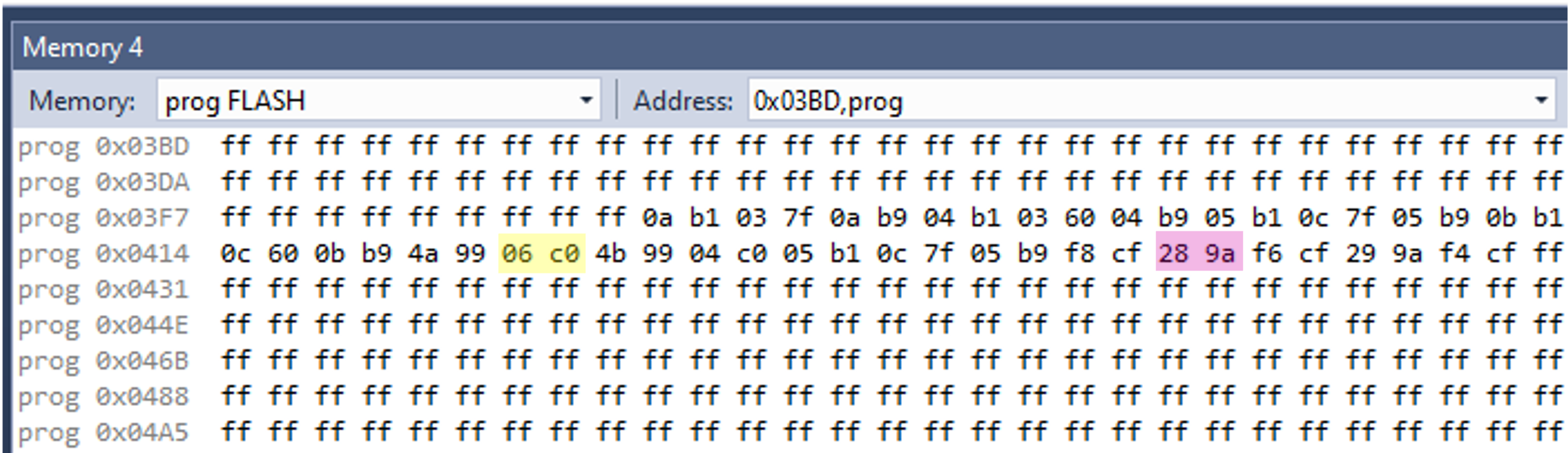

Relative Addressing Example

Figure 10: An example to illustrate relative addressing

RJMP LED1 -> 1100 kkkk kkkk kkkkis

C006 = 1100 0000 0000 0110 -> RJMP +6

Figure 11: The program counter jumps 6 memory locations forward.

Summary

In this section have reviewed different addressing modes supported by the AVR instruction set commenting on use cases and speed (in clock cycles) of their operation.

On Canvas

You should review Section 3 of the AVR instructions set manual (Atmel 2020) on program and data addressing modes. There is a short quiz covering the content of this chapter.

Next Time - Class Test!

In preparation for the class test next week, you should review all the content covered in these lecture notes, self-directed study material and the lab classes.

Note that the class test is closed-book but you have will access to the reference manuals mentioned in these notes.

Footnotes

In inherent addressing the effective address that the operation acts on is the register itself.

The

dinRdis a number in the range 0-31.The

rinRris also a number in the range 0-31.Note: in these examples, the labels

PINDandPORTCmust have already been defined.the value of the second operand of an operator with immediate addressing will be hard coded into the code and cannot be changed during the running of a program.